JOSÉ FERNÁNDEZ RAMOS JOSÉ LUIS DÍAZ LAFUENTE JORGE ROMERO SÁNCHEZ

# DISPOSITIVOS ELECTRÓNICOS PARA ESTUDIANTES DE INFORMÁTICA

UNIVERSIDAD DE MÁLAGA / MANUALES

## JOSÉ FERNÁNDEZ RAMOS JOSÉ LUIS DÍAZ LAFUENTE JORGE ROMERO SÁNCHEZ

# DISPOSITIVOS ELECTRÓNICOS PARA ESTUDIANTES DE INFORMÁTICA

Segunda reimpresión, 2004 Primera reimpresión, 2002 Primera edición, 2001

© Los autores

© Publicaciones y Divulgación Científica. Universidad de Málaga.

Diseño de la colección: J. M. Mercado

ISBN: 84-7496-853-4

Depósito Legal: MA-105/2001

Imprime: Imagraf Impresores, S.A. Tel.: 952 32 85 97

Divulgación Científica

Esta obra está bajo una licencia de Creative Commons Reconocimiento-NoComercial-SinObraDerivada 4.0 Internacional: http://creativecommons.org/licenses/by-nc-nd/4.0/legalcode Cualquier parte de esta obra se puede reproducir sin autorización pero con el reconocimiento y atribución de los autores. No se puede hacer uso comercial de la obra y no se puede alterar, transformar o hacer obras derivadas.

## INDICE

| 1 Nociones básicas de Teoría de Circuit | Teoría de C | es básicas d | L- Nociones | 1 |

|-----------------------------------------|-------------|--------------|-------------|---|

|-----------------------------------------|-------------|--------------|-------------|---|

| MAGNITUDES ELÉCTRICAS Y CONCEPTOS FUNDAMENTALES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

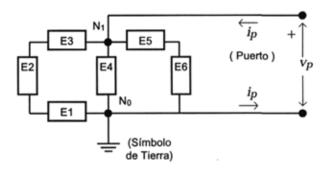

| Conceptos básicos de circuitos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3  |

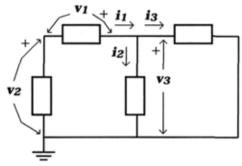

| Leyes de Kirchoff.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

| Potencia Eléctrica.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5  |

| ELEMENTOS BÁSICOS DE CIRCUITO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

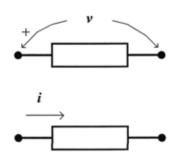

| Elementos pasivos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

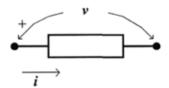

| Resistencia lineal u óhmica.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6  |

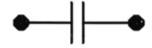

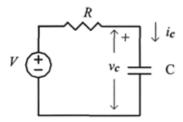

| Condensador.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6  |

| Inductancia.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

| Elementos activos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7  |

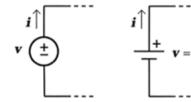

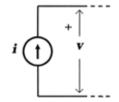

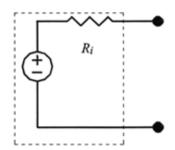

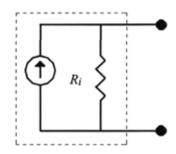

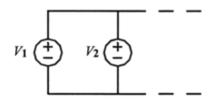

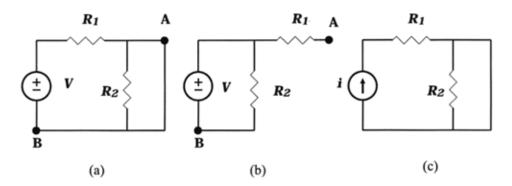

| Fuentes independientes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7  |

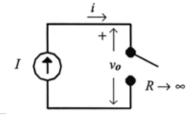

| Fuentes controladas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

| Modelado de elementos de circuito no lineales.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |

| ANÁLISIS DE CIRCUITOS. ANÁLISIS DEL PUNTO DE OPERACIÓN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 |

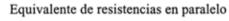

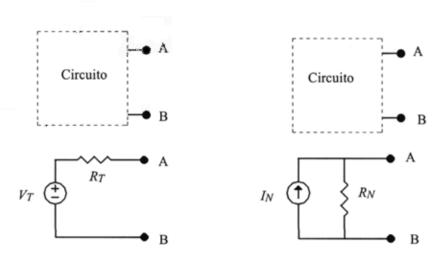

| Métodos alternativos de análisis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

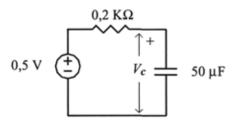

| ANÁLISIS DE CIRCUITOS. ANÁLISIS TRANSITORIOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13 |

| EJERCICIOS RESUELTOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

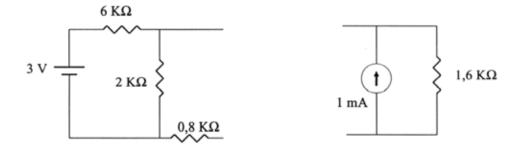

| Circuitos básicos con resistencias.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 |

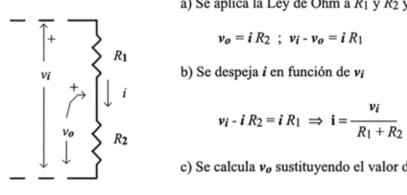

| Divisor de Tension.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 |

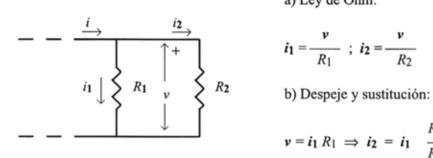

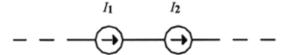

| Divisor de Intensidad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

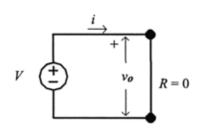

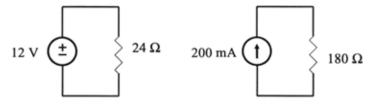

| Circuitos imposibles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

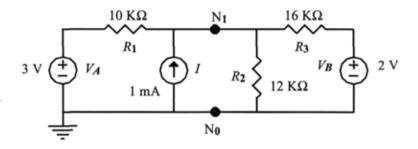

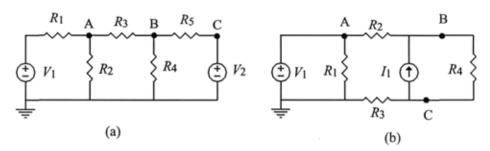

| Análisis de circuitos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18 |

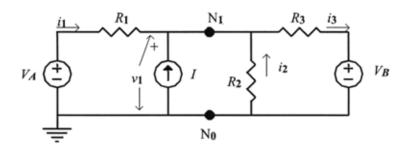

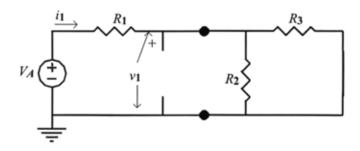

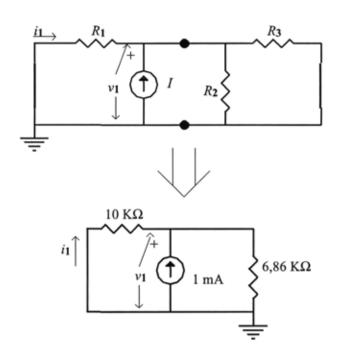

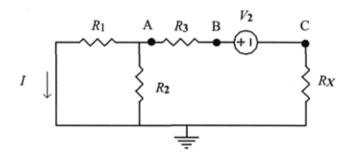

| Circuito con fuentes independientes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

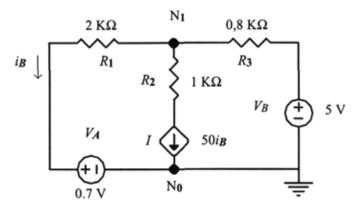

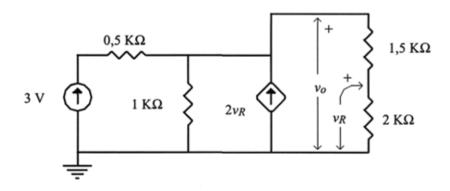

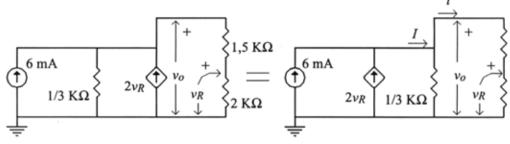

| Circuito con fuentes controladas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

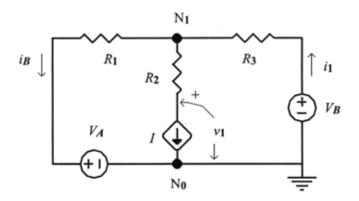

| Circuito con fuentes controladas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

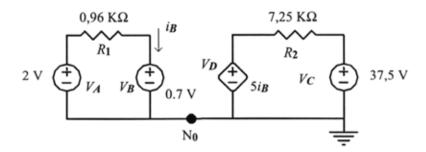

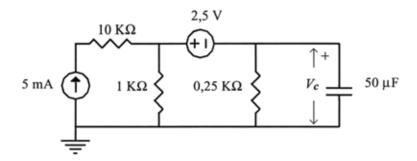

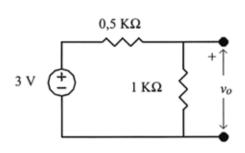

| Método de Superposición.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |

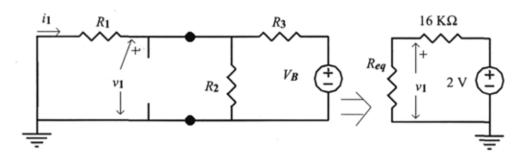

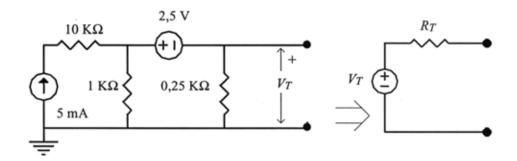

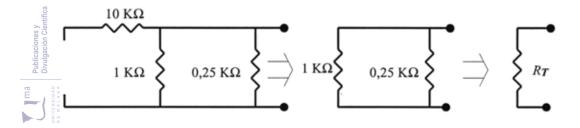

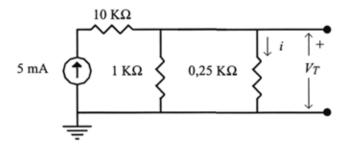

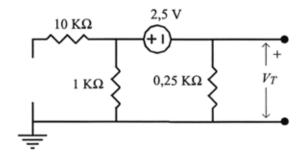

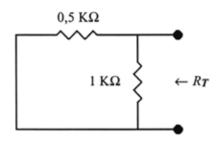

| Método de cálculo de equivalentes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

| 2 Conceptos básicos de circuitos digitales                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

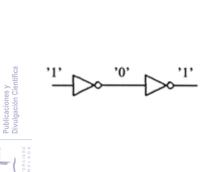

| SEÑALES ELÉCTRICAS FAMILIAS LÓGICAS CARACTERIZACIÓN DE FAMILIAS LÓGICAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

| FAMILIAS LÓGICAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34 |

| CARACTERIZACIÓN DE FAMILIAS LÓGICAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

| DOMINE WORK OF THE PROPERTY OF |    |

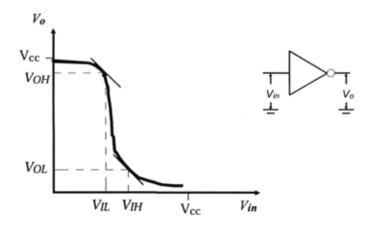

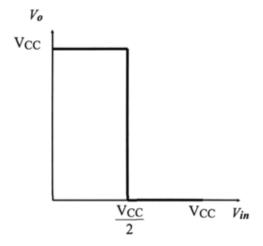

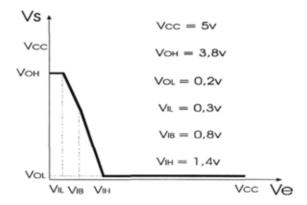

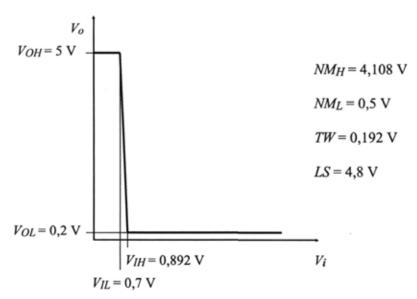

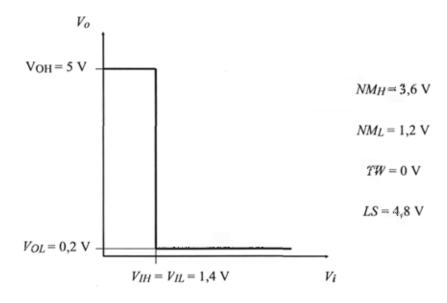

| Característica de transferencia                                | 35 |

|----------------------------------------------------------------|----|

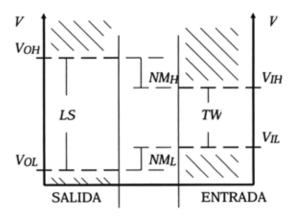

| Características de entrada-salida.                             | 36 |

| Inmunidad al ruido.                                            | 37 |

| Consumo de energía.                                            | 37 |

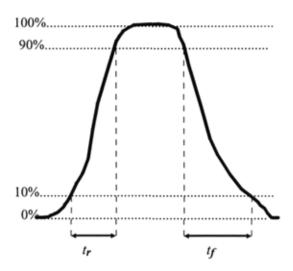

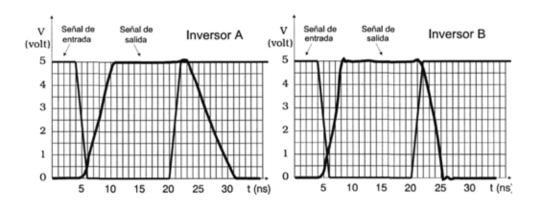

| e) Velocidad de operación.                                     | 38 |

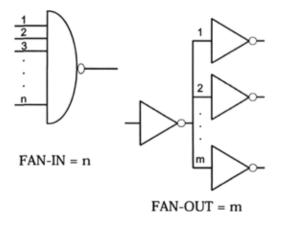

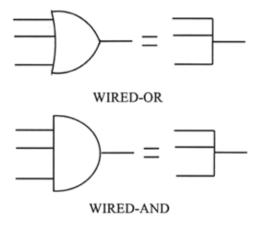

| f) Flexibilidad lógica.                                        | 40 |

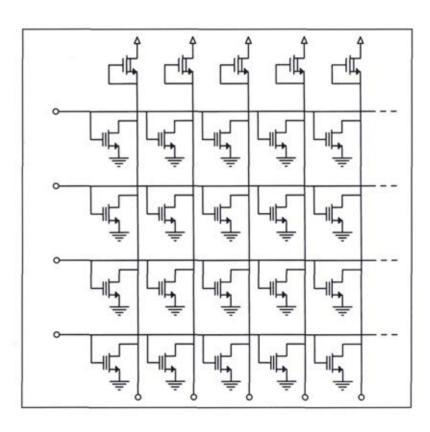

| g) Capacidad de integración.                                   | 41 |

| LA FAMILIA LÓGICA IDEAL.                                       | 41 |

| 3 Semiconductores                                              |    |

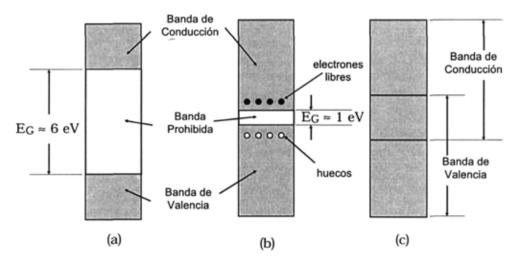

| ESTRUCTURA DE LOS SÓLIDOS.                                     | 45 |

| Aislantes.                                                     | 46 |

| Conductores.                                                   | 46 |

| Semiconductores.                                               | 47 |

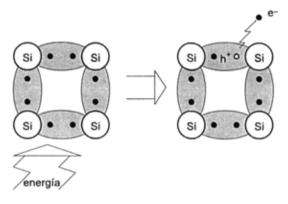

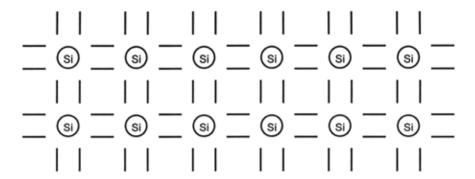

| PORTADORES DE CARGA EN SEMICONDUCTORES.                        | 48 |

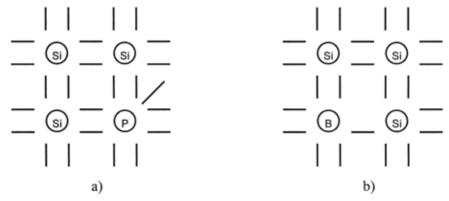

| SEMICONDUCTORES INTRÍNSECOS Y EXTRÍNSECOS.                     | 50 |

| Ley de acción de masas                                         | 51 |

| Ecuación de neutralidad de carga                               | 52 |

| Concentración de portadores                                    | 52 |

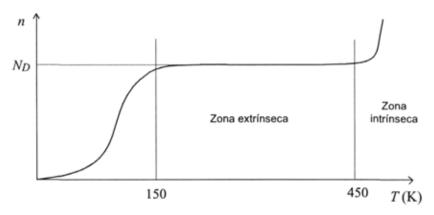

| Influencia de la temperatura en la concentración de portadores | 54 |

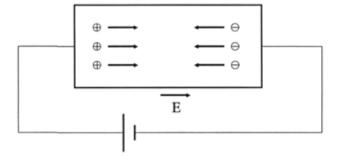

| MOVIMIENTOS DE PORTADORES                                      | 55 |

| Fenómenos de arrastre.                                         | 55 |

| Fenómenos de difusión.                                         | 57 |

| Fenómenos de Generación - Recombinación.                       | 58 |

| 4 El diodo de unión P-N                                        |    |

| INTRODUCCIÓN                                                   | 61 |

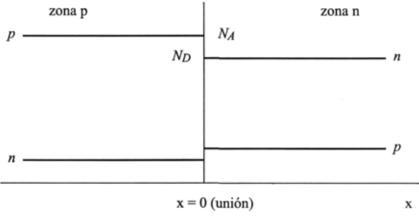

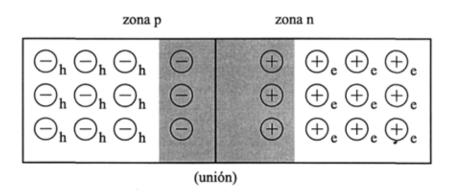

| LA UNION P-N EN EQUILIBRIO                                     | 61 |

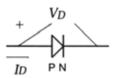

| EL DIODO DE UNIÓN P-N                                          | 64 |

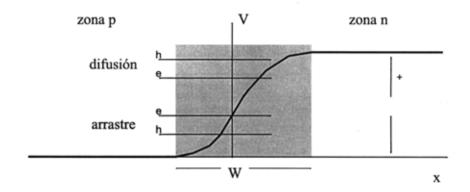

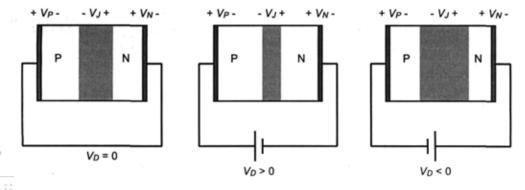

| Polarización nula.                                             | 65 |

| Polarización directa.                                          | 66 |

| Polarización inversa.                                          | 66 |

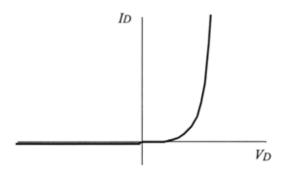

| CURVA CARACTERÍSTICA DEL DIODO.                                | 66 |

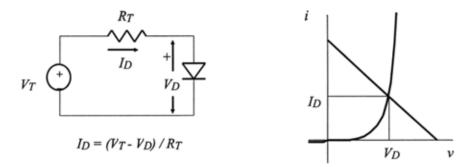

| EL DIODO COMO ELEMENTO DE CIRCUITO                             | 67 |

| Métodos analíticos.                                            | 67 |

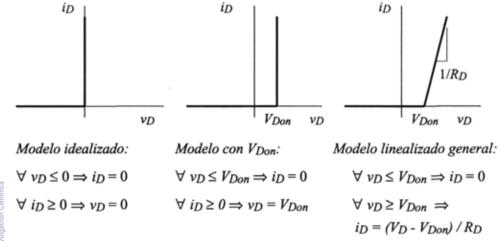

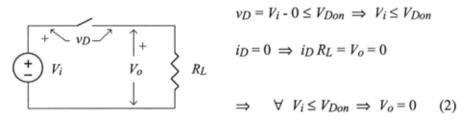

| Modelo idealizado.                                             | 68 |

| Modelo con tensión umbral.                                     | 68 |

| Modelo linealizado general.                     | 68  |

|-------------------------------------------------|-----|

| Métodos gráficos.                               | 69  |

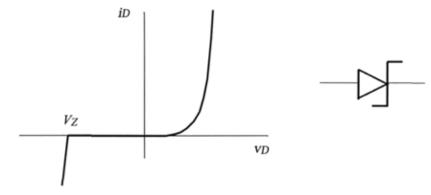

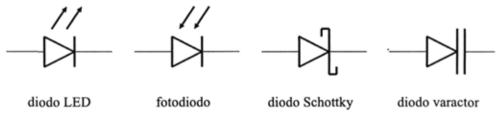

| OTROS TIPOS DE DIODOS.                          | 69  |

| El diodo Zener.                                 | 69  |

| Diodos varactores                               | 71  |

| Diodos emisores de luz ( LED ).                 | 72  |

| Fotodiodos.                                     | 72  |

| Diodos Schottky.                                | 73  |

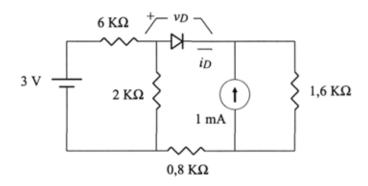

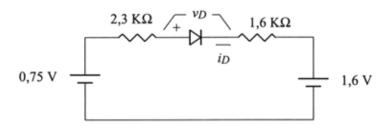

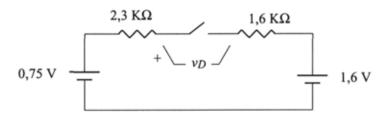

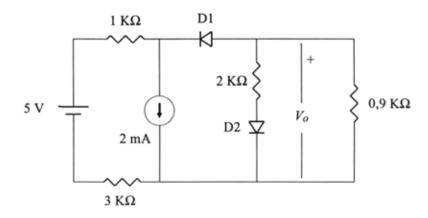

| EJERCICIOS RESUELTOS                            | 73  |

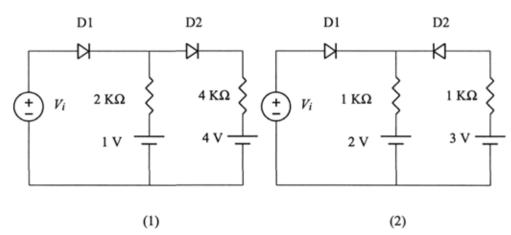

| Ejercicios de cálculo del punto de trabajo.     | 73  |

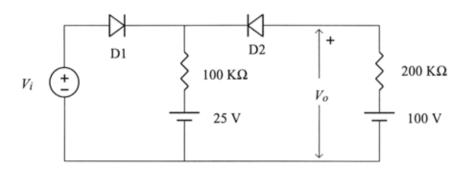

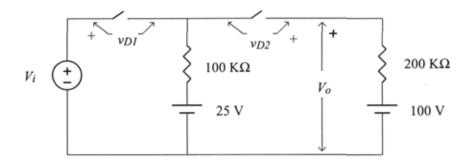

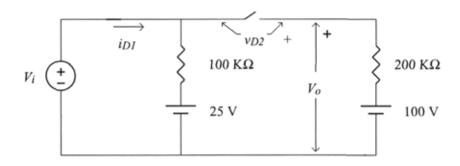

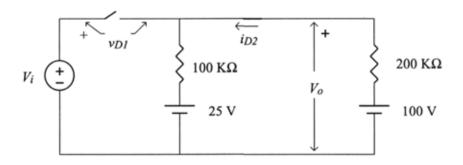

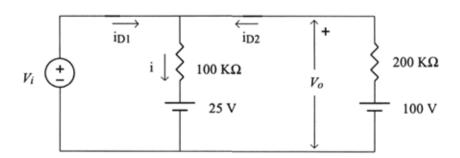

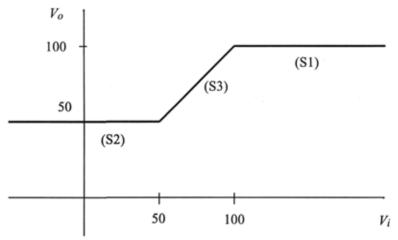

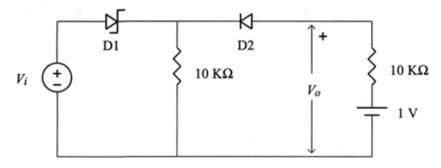

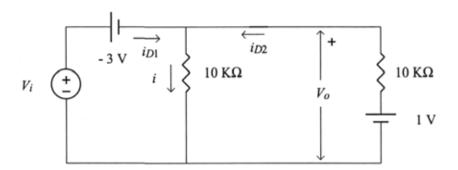

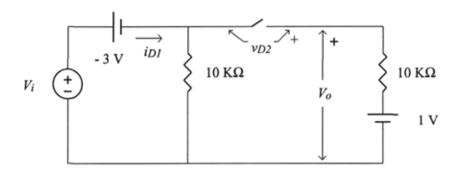

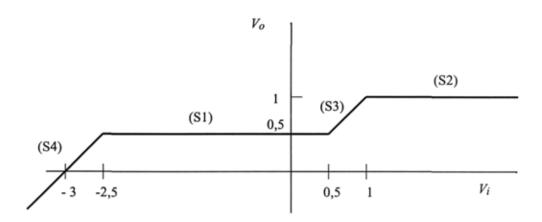

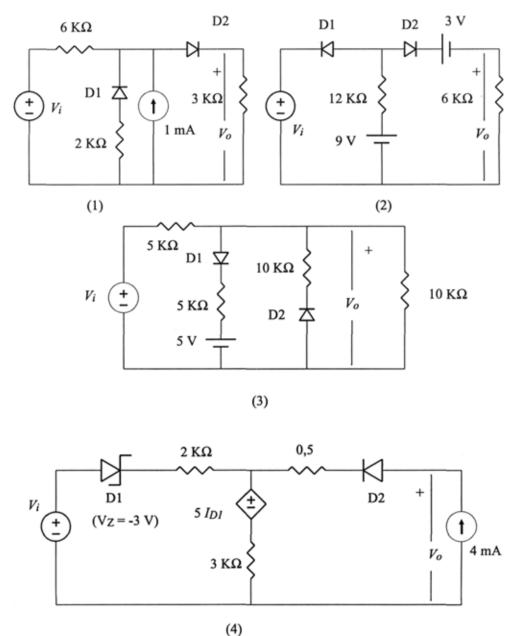

| Ejercicios de característica de transferencia.  | 80  |

| 5 El transistor bipolar (B.J.T.)                |     |

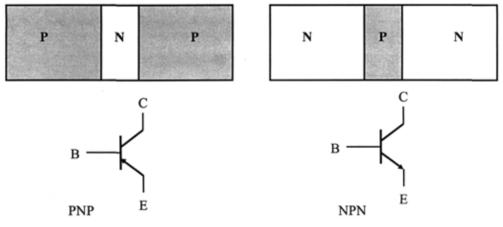

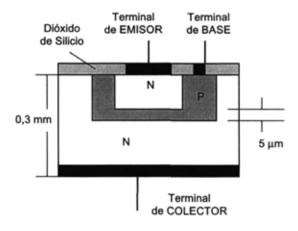

| ESTRUCTURA FÍSICA DEL B.J.T.                    | 93  |

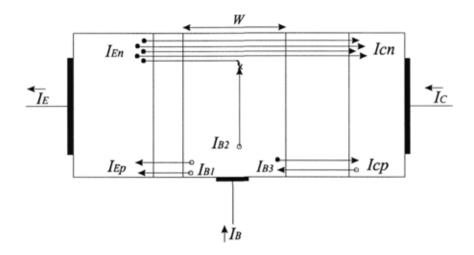

| FUNCIONAMIENTO DEL B.J.T.                       | 94  |

| REGIONES DE FUNCIONAMIENTO DEL B.J.T.           | 97  |

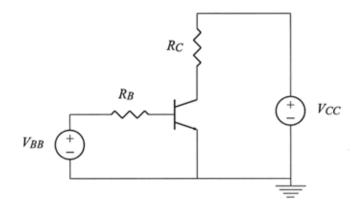

| EL TRANSISTOR BIPOLAR COMO ELEMENTO DE CIRCUITO | 98  |

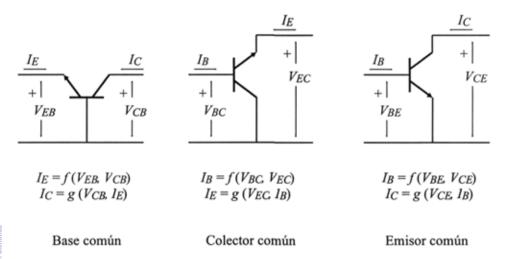

| Configuraciones del transistor bipolar          | 99  |

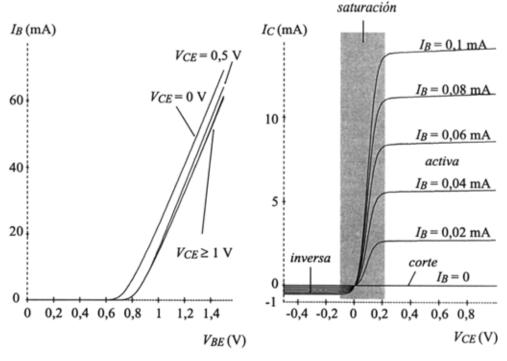

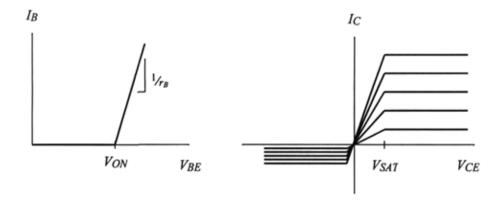

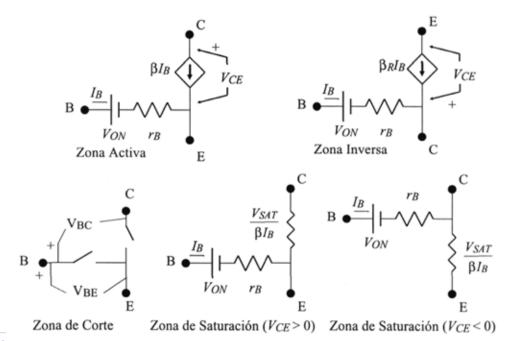

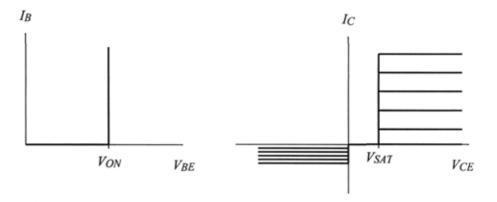

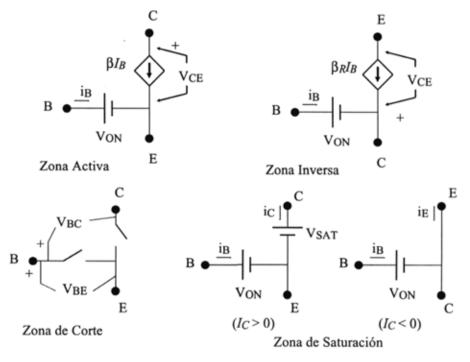

| Curvas Características del Transistor Bipolar   | 100 |

| Polarización y modelos linealizados del B.J.T.  | 101 |

| Modelo linealizado general.                     | 102 |

| Modelo idealizado.                              | 103 |

| Modelo simplificado                             | 104 |

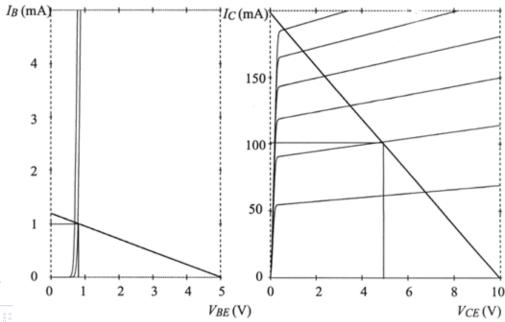

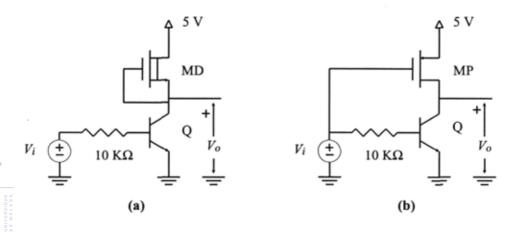

| EL TRANSISTOR BIPOLAR EN CONMUTACIÓN            | 107 |

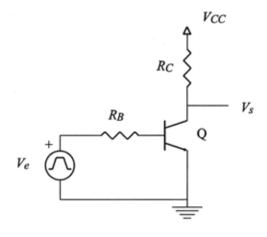

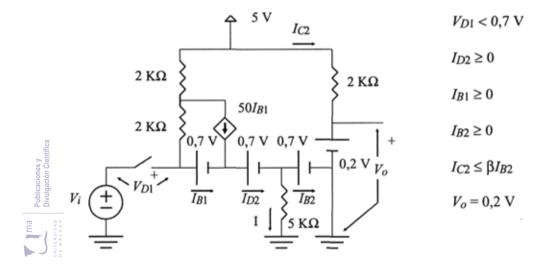

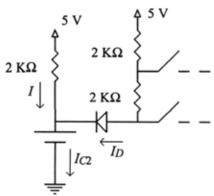

| Familias Lógicas Bipolares                      | 108 |

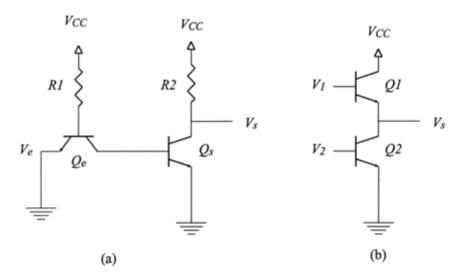

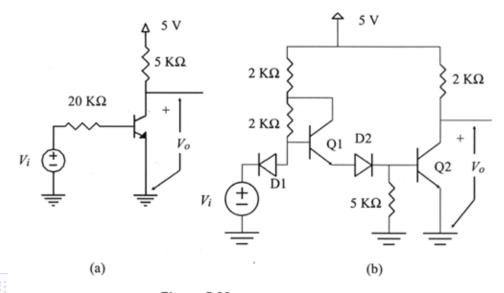

| Familia RTL (Resistor - Transistor Logic).      | 108 |

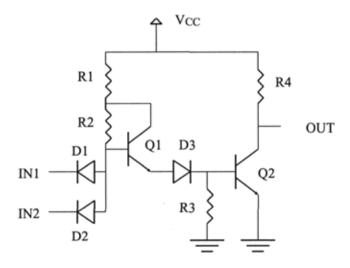

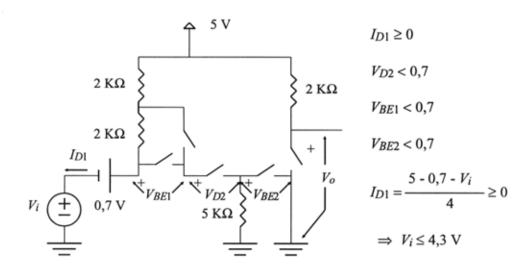

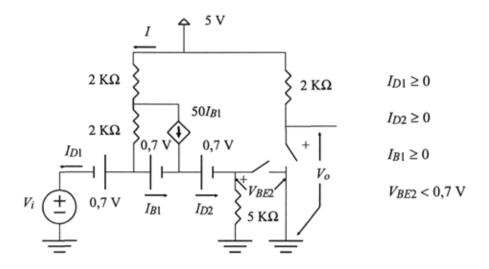

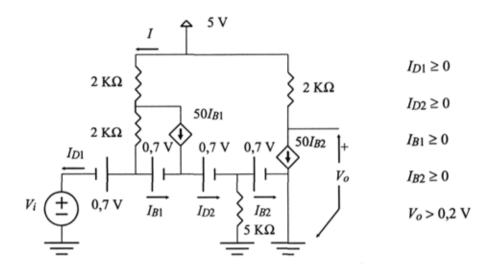

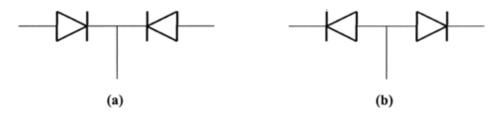

| Familia DTL (Diode Transistor logic)            | 109 |

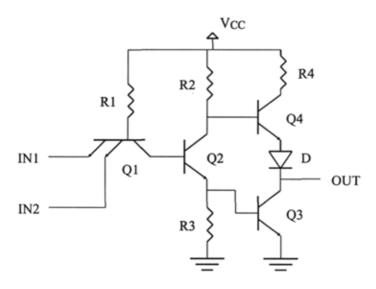

| Familia TTL ( Transistor Transistor Logic )     | 111 |

| EJERCICIOS RESUELTOS                            | 116 |

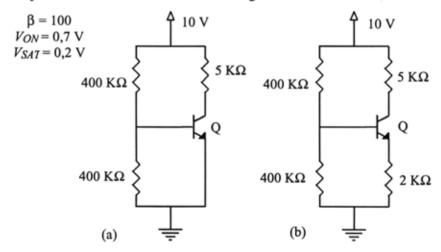

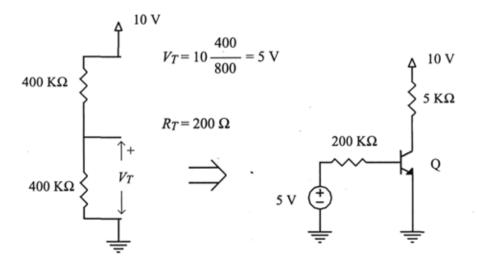

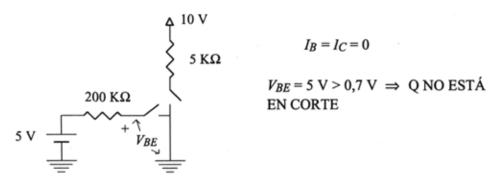

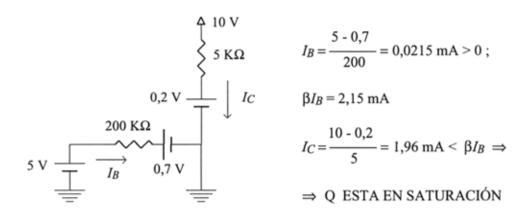

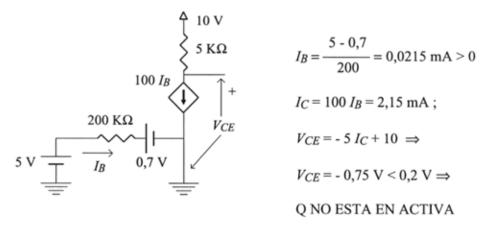

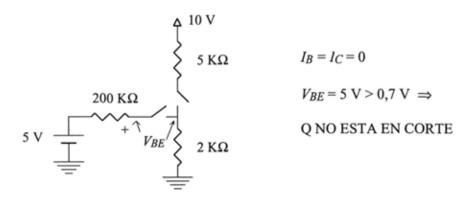

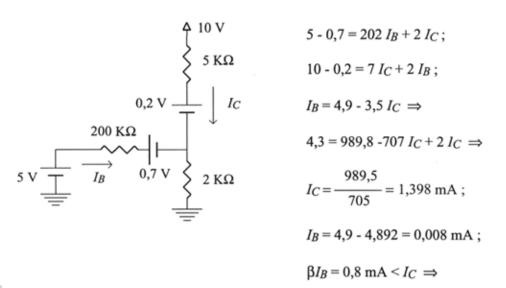

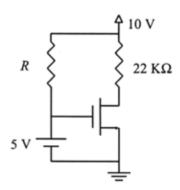

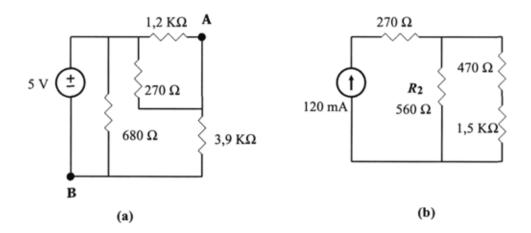

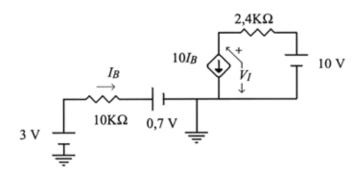

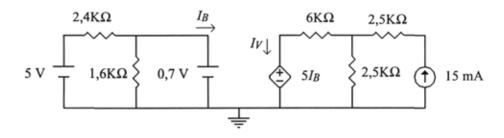

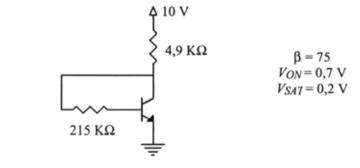

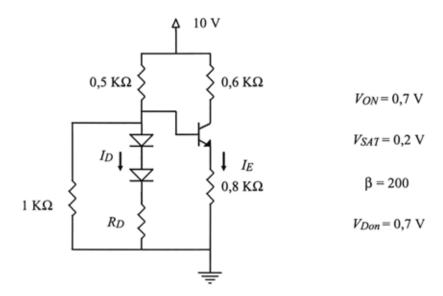

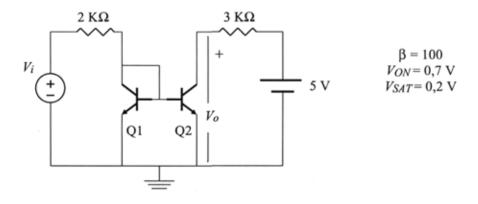

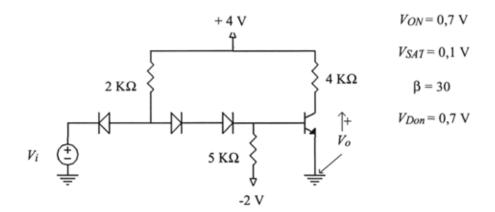

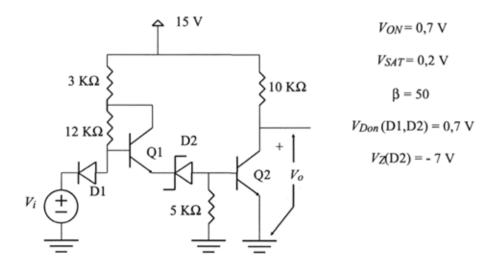

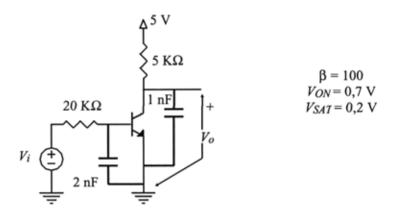

| Ejercicios de cálculo del punto de trabajo.     | 116 |

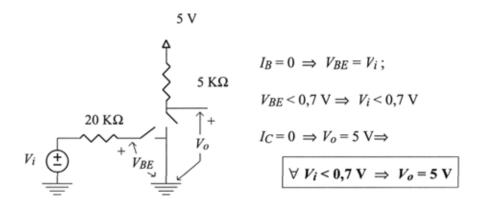

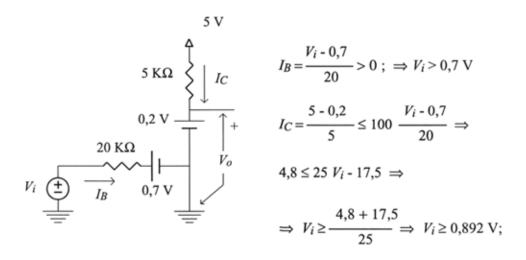

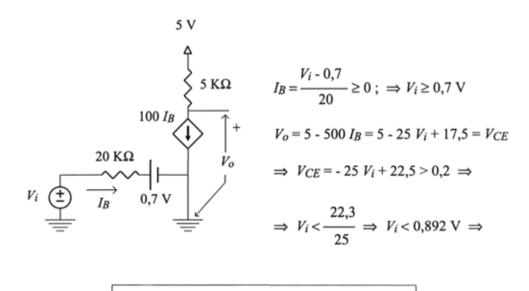

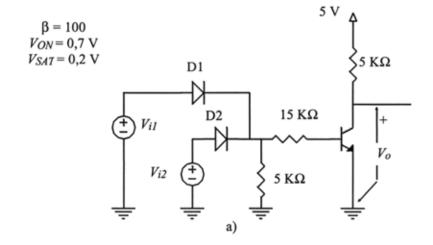

| Ejercicios de característica de transferencia.  | 124 |

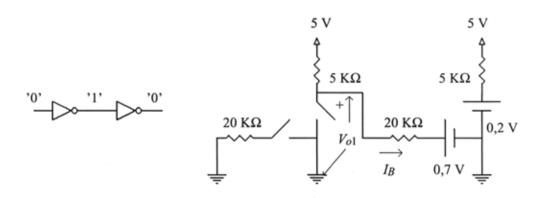

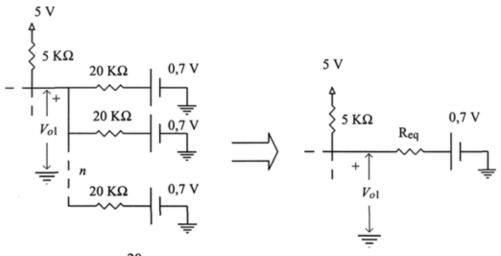

| Ejercicios de cálculo del FAN-OUT.              | 131 |

| 6 El transistor M.O.S.F.E.T.                    |     |

| INTRODUCCIÓN                                    | 137 |

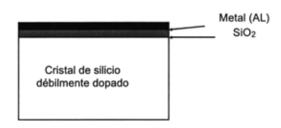

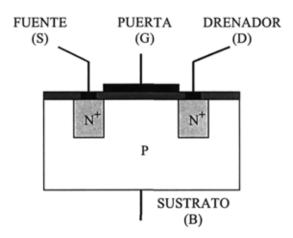

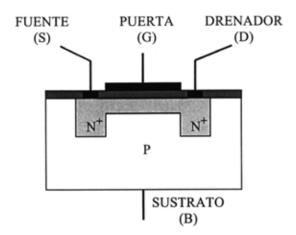

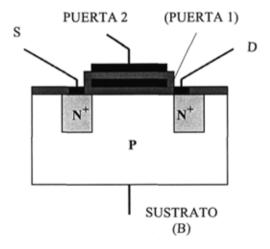

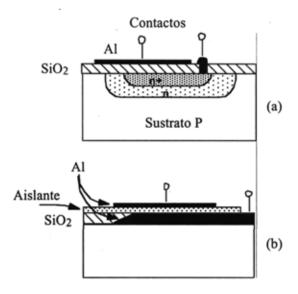

| LA ESTRUCTURA M.O.S.                            | 137 |

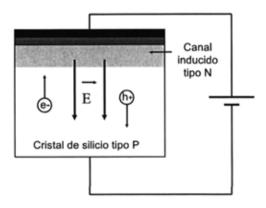

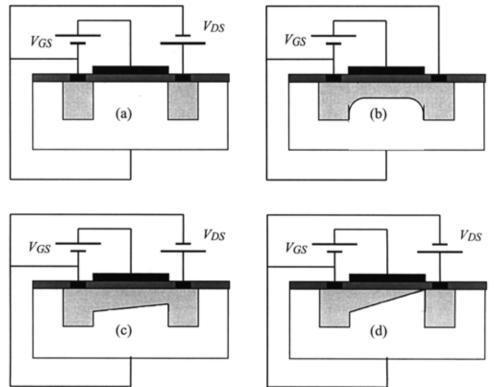

| MOSFET DE ACUMULACIÓN O ENRIQUECIMIENTO         | 138 |

iv INDICE

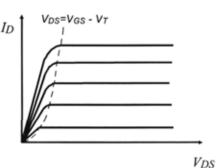

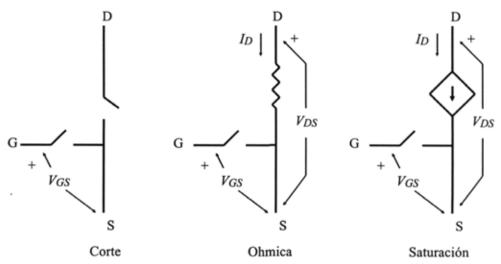

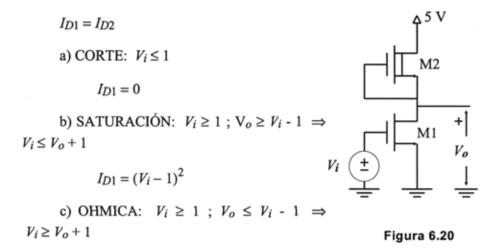

| Zona de Corte                                                             | 141 |

|---------------------------------------------------------------------------|-----|

| Zona Ohmica                                                               | 142 |

| Zona de Saturación                                                        | 143 |

| MOSFET DE DEPLEXIÓN O EMPOBRECIMIENTO                                     | 143 |

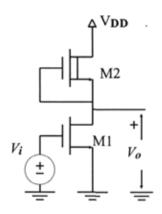

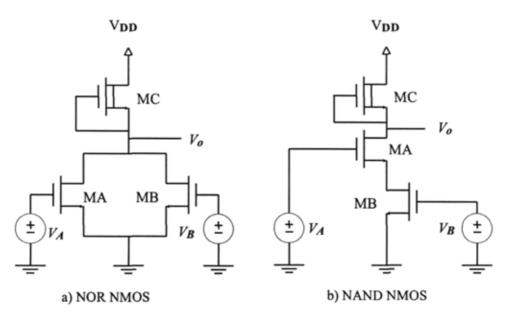

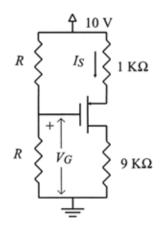

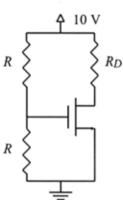

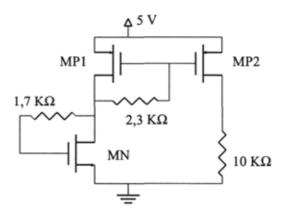

| FAMILIA LÓGICA NMOS                                                       | 144 |

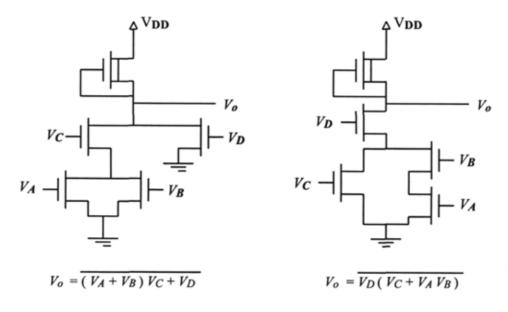

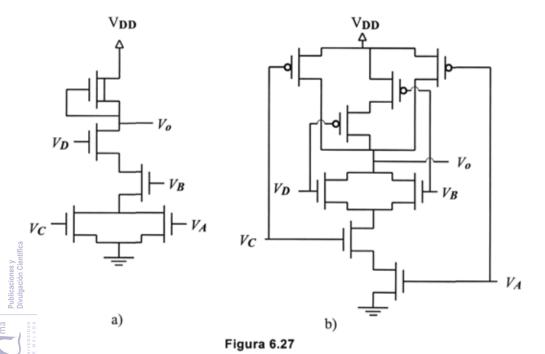

| Funciones lógicas NMOS                                                    | 147 |

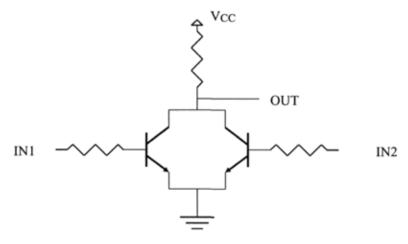

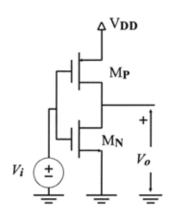

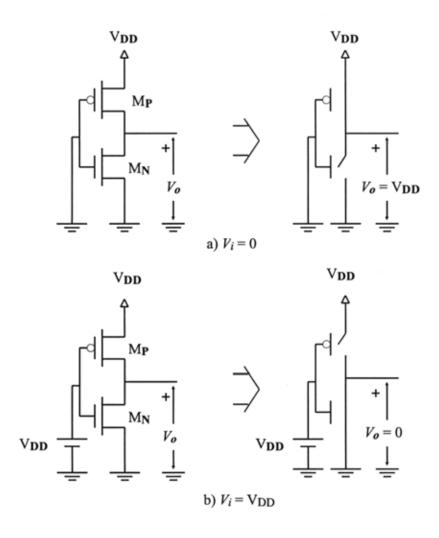

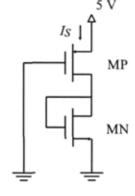

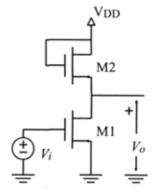

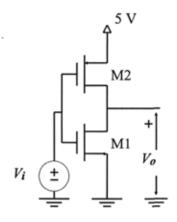

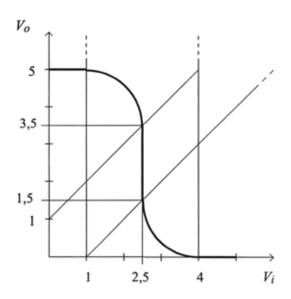

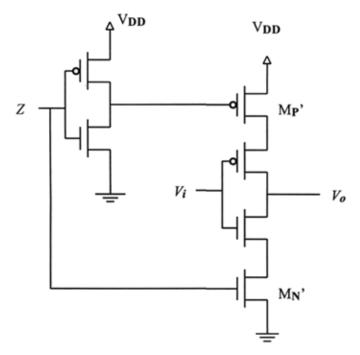

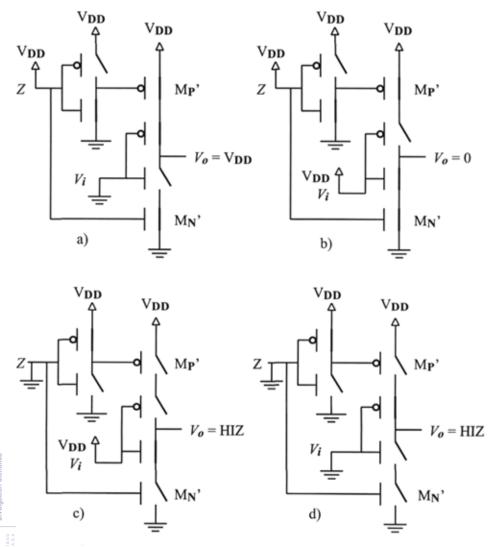

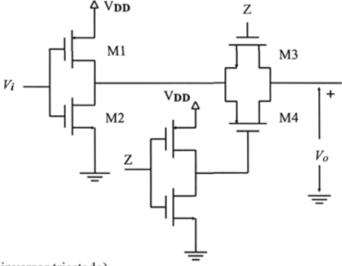

| FAMILIA LÓGICA CMOS                                                       | 149 |

| Modelo simplificado de la estructura CMOS                                 | 150 |

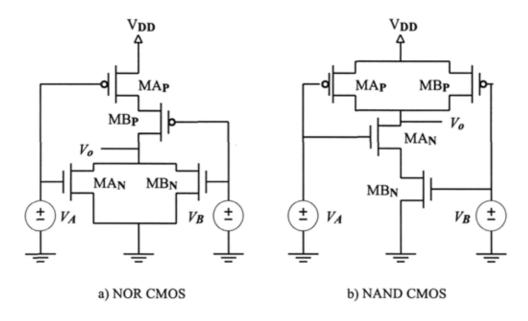

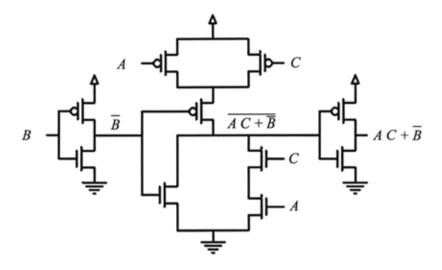

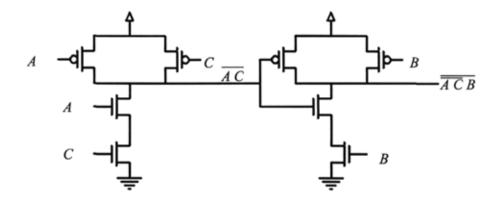

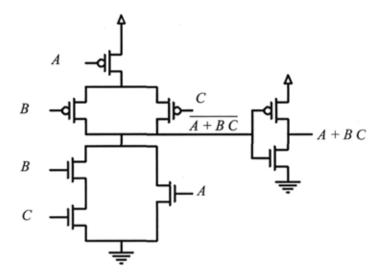

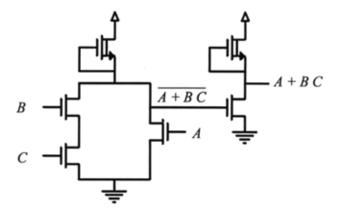

| Funciones lógicas con CMOS                                                | 150 |

| EJERCICIOS RESUELTOS                                                      | 151 |

| Ejercicios de cálculo del punto de trabajo                                | 151 |

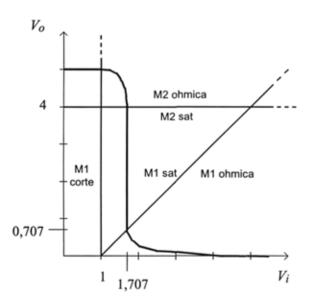

| Ejercicios de característica de transferencia                             | 158 |

| Ejercicios de análisis de la función lógica que realiza un circuito.      | 170 |

| Ejercicios de síntesis de una función lógica estándar NMOS o CMOS.        | 173 |

| 7 Memorias de estado sólido                                               |     |

| INTRODUCCIÓN                                                              | 179 |

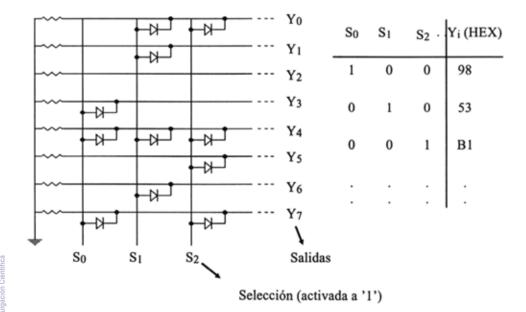

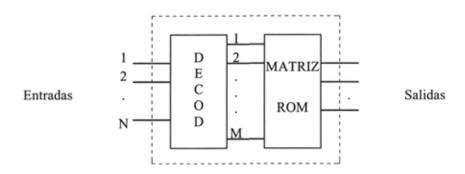

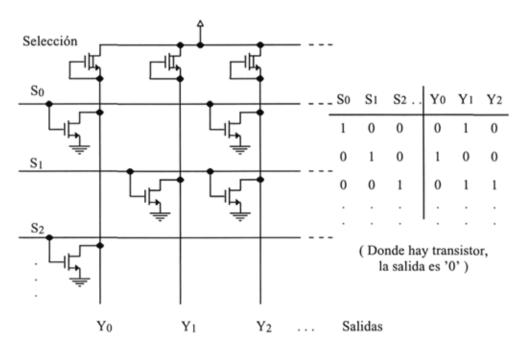

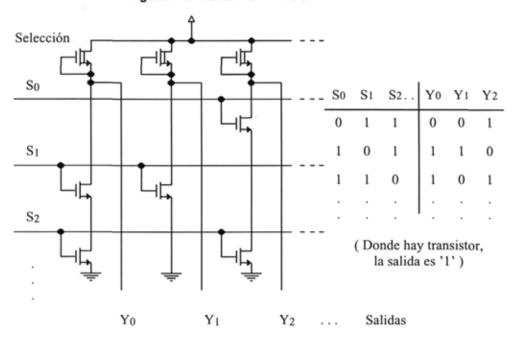

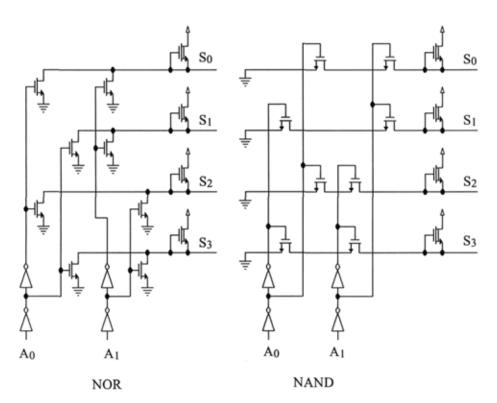

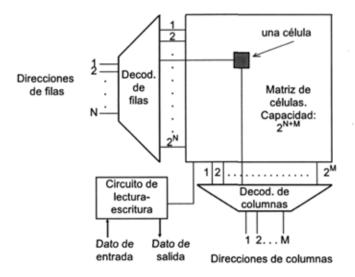

| MEMORIAS ROM                                                              | 179 |

| Decodificadores para ROM                                                  | 183 |

| Otros tipos de ROM                                                        | 183 |

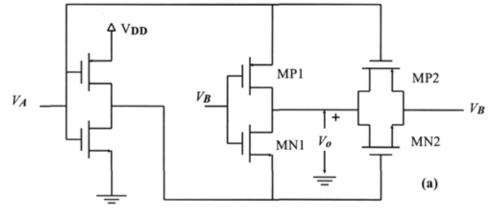

| MEMORIAS RAM.                                                             | 185 |

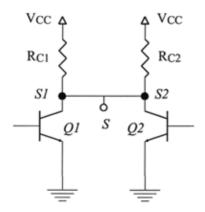

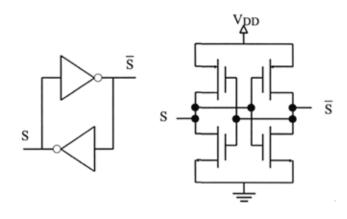

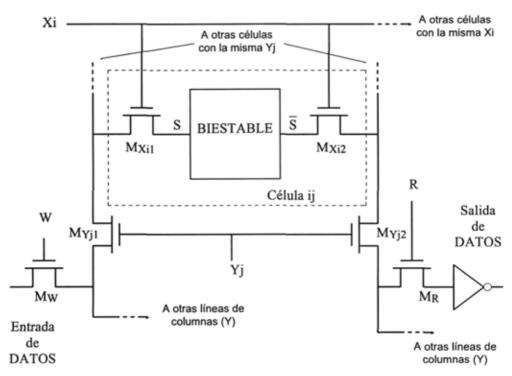

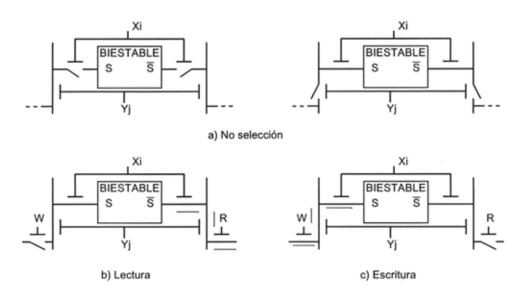

| Memoria RAM estática.                                                     | 188 |

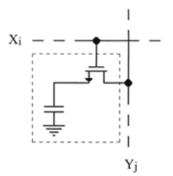

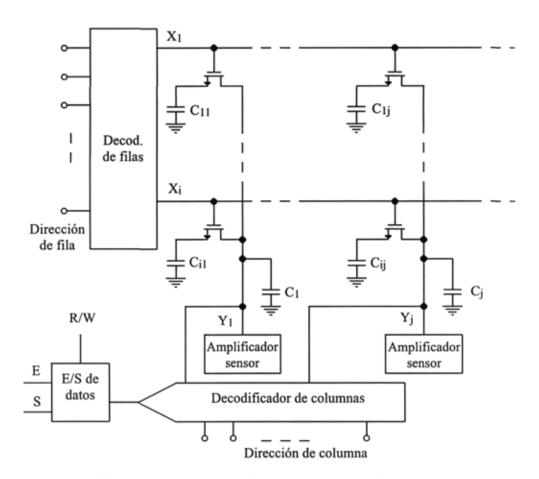

| Memoria RAM dinámica                                                      | 189 |

| Memoria RAM estática.                                                     | 188 |

| Memoria RAM dinámica                                                      | 189 |

| 8 Procesos tecnológicos de fabricación de circuitos integrados            |     |

| INTRODUCCIÓN A LOS PROCESOS TECNOLÓGICOS.                                 | 195 |

| CRECIMIENTO CRISTALINO Y PREPARACIÓN DE OBLEAS.                           | 196 |

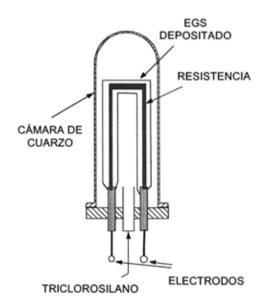

| Obtención del Silicio electrónico (EGS: Electronic-Grade Silicon).        | 196 |

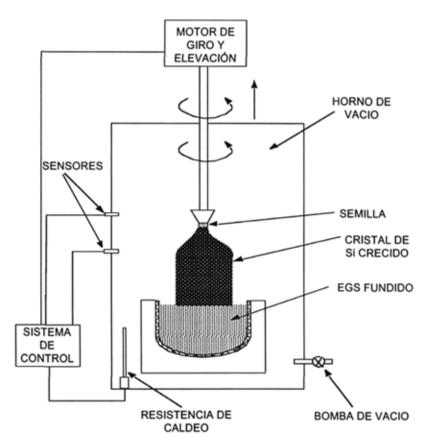

| Generación del Silicio cristalino: la técnica de crecimiento Czochralski. | 197 |

| Obtención de obleas.                                                      | 198 |

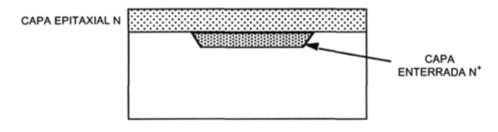

| CRECIMIENTO EPITAXIAL.                                                    | 199 |

| DEPOSICIÓN DE CAPAS AISLANTES.                                            | 200 |

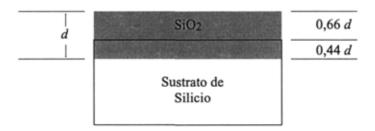

| OXIDACIÓN.                                                                | 201 |

| DIFUSIÓN.                                                                 | 201 |

| IMPLANTACIÓN IÓNICA                                                       | 203 |

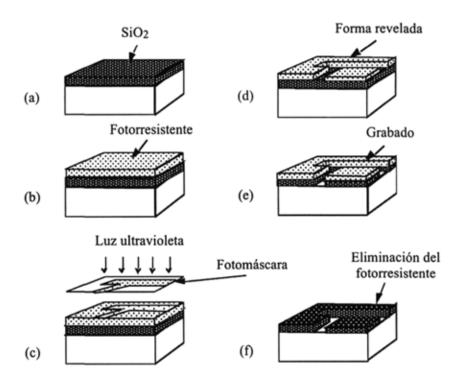

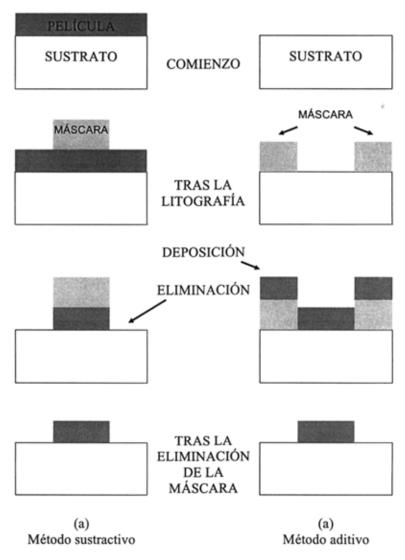

| LITOGRAFIA.                                                       | 203 |

|-------------------------------------------------------------------|-----|

| GRABADO.                                                          | 205 |

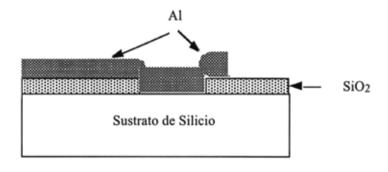

| METALIZACIÓN.                                                     | 208 |

| PROCESOS DE INTEGRACIÓN DE UN CIRCUITO.                           | 209 |

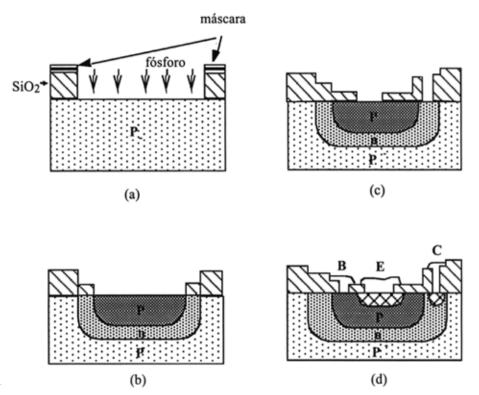

| Procesos básicos en tecnología bipolar.                           | 209 |

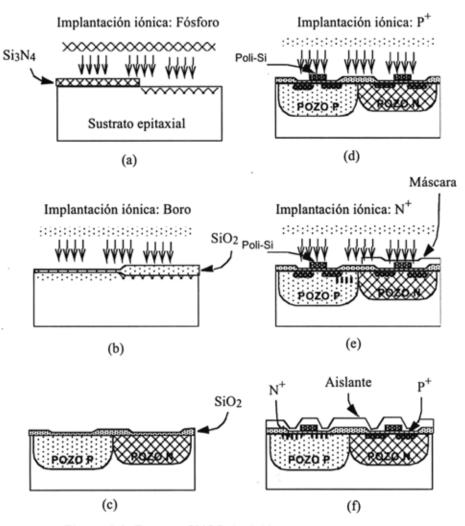

| Procesos básicos en tecnología MOS.                               | 210 |

| Integración de componentes pasivos: resistencias y condensadores. | 212 |

| TÉCNICAS DE ENCAPSULADO Y ENSAMBLADO DE CIs.                      | 213 |

| HERRAMIENTAS DE DISEÑO ASISTIDO POR COMPUTADOR.                   | 214 |

| APÉNDICE A Cuestionarios de trabajo                               |     |

| ANÁLISIS DE CIRCUITOS                                             | 219 |

| CIRCUITOS DIGITALES                                               | 225 |

| SEMICONDUCTORES Y DIODO                                           | 227 |

| TRANSISTOR BIPOLAR                                                | 234 |

| TRANSISTOR MOSFET                                                 | 242 |

| MEMORIAS                                                          | 240 |

vi Prólogo

## PRÓLOGO

El presente manual surge de la experiencia didáctica de los autores, profesores del Departamento de Electrónica de la Universidad de Málaga, con el objetivo de proporcionar a los alumnos de los primeros cursos de las Escuelas de Ingeniería Informática unos conocimientos sobre los Dispositivos Electrónicos adaptados tanto en contenidos como en profundidad a las necesidades de su especialidad.

La mayor parte de la bibliografía sobre Dispositivos Electrónicos está compuesta por obras extensas, que cubren en mayor o menor medida todo su campo de aplicaciones, tanto analógicas como digitales. Esta visión tiene la ventaja de ofrecer una perspectiva bastante completa de la electrónica moderna, pero para el alumno que se enfrenta por primera vez a la materia, la gran cantidad de información puede suponer una dificultad importante en la distinción de los conceptos que son realmente básicos de los que no lo son.

Con este manual pretendemos separarnos de esta tendencia, incluyendo únicamente los contenidos teóricos que consideramos imprescindibles, centrados en una descripción mínima de la estructura física y del funcionamiento a nivel microscópico de los dispositivos de estado sólido, junto con los modelos que permiten analizar el comportamiento de estos dispositivos cuando forman parte de un circuito electrónico.

Se le ha dado especial importancia a la descripción de los métodos de análisis de circuitos electrónicos, fundamentalmente el análisis del punto de operación y de la característica de transferencia estática, junto con una introducción al análisis transitorio. No se han incluído los análisis de respuesta en frecuencia y de pequeña señal por ser menos importantes para el estudio de los circuitos digitales. En todo momento se ha tratado de sistematizar al máximo todo el proceso de análisis de circuitos, para evitar en lo posible que la solución de un problema o la comprensión del funcionamiento de un determinado circuito dependan de la aparición de una "idea feliz", hecho que no suele ser muy frecuente en el alumno inexperto.

Como pieza clave para la comprensión de estos métodos de análisis, el grueso de la mayoría de los capítulos está formado por una gran cantidad de **Ejercicios Resueltos**, en los que se muestra paso a paso el desarrollo de dichos métodos en la solución de los problemas. El complemento final a los contenidos del manual lo forman los **Cuestionarios de Trabajo** del Apéndice A. Más que una lista de ejercicios propuestos, estos cuestionarios tratan de ser una guía que oriente el estudio del alumno, proponiéndole cuestiones y problemas de complejidad creciente que

sirvan para que él mismo calibre el grado de comprensión que va adquiriendo en cada capítulo.